Building a modular, functional and efficient software-hardware stack is crucial for future deployment and integration of quantum accelerators (chips). Instruction Set Architecture (ISA) acts as a contract between hardware and software. Existing ISAs (x86, ARM, MIPS) are designed for general purpose computing and do not address the needs of quantum computing and control.

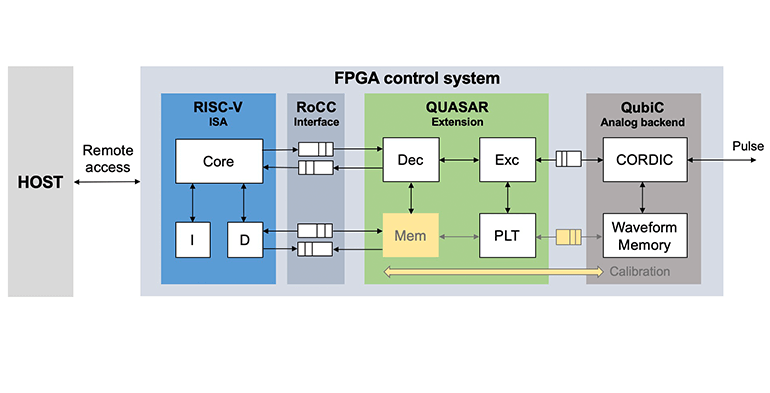

We study those needs of quantum computing and control for NISQ and beyond-NISQ scenarios to facilitate quantum device adoption at the system-level. We implement critical functionalities in hardware as highly specialized modular blocks that can be easily extended and scaled up. Namely, we develop a quantum ISA extension (QUASAR) and demonstrate its capabilities and limitations on a real FPGA platform.

What We Did

We have developed an evaluation methodology based on statistical characterization of quantum circuits that allows us to understand the capabilities and limitations of control hardware.

We have designed two quantum extensions (QUASAR and qV) to the RISC-V ISA to enable efficient quantum circuit encoding. We implemented the QUASAR extension as a soft-core (ICE) and as a co-processor through the RoCC interface.

We integrated the QUASAR co-processor with the QubiC control backend and a 64-bit RISC-V core into a complete system on an FPGA. The system executes Linux and is accessible via remote control to provide a new control experience to the user.

All our implementations, both hardware and software, will be publicly available for the community (subject to the DOE approval).

Current Status & Next Steps

In the current version of the system, control pulses are stored in a Pulse Library Table (PLT) hardware module. That approach allows fast execution of the pre-defined pulses. We plan to extend the PLT functionality with dynamic pulse shaping. Moreover, we plan to implement a read-out post-processing module on hardware to allow additional research in the direction of quantum state measurement.