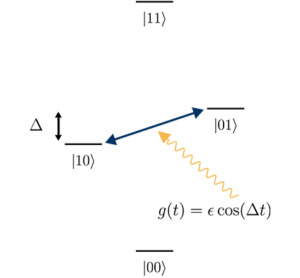

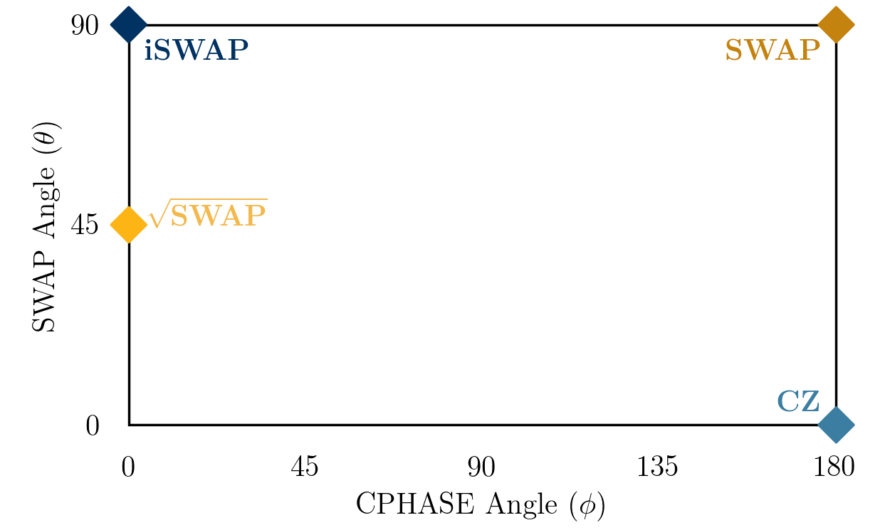

While high fidelity two qubit gates have been achieved on superconducting circuit platforms in recent years, two qubit gate fidelity remains a limiting factor for algorithm performance in the NISQ era. All microwave gates implemented on fully static architectures are simple to implement and allow for high coherence qubits, but this comes at the expense of always-on couplings and slower gate times. Fully tunable architectures, on the other hand, trade minimal residual coupling and fast entangling operations for increased complexity and sensitivity to flux noise. Parametric entangling gates, which use fast flux modulation to induce resonant interactions in a rotating frame, offer a middle ground between these two approaches to high fidelity two qubit gates. By restricting tunability to a coupling element, qubit sensitivity to flux noise can be significantly reduced and high coherence maintained. Furthermore, the resonant nature of the parametric interactions allow for fast entangling gates with minimal residual coupling. At AQT, we are working towards implementing parametric entangling gates on a 10 qubit quantum processor and investigating how error sources can be mitigated to achieve gate fidelities beyond the current state-of-the-art.

While high fidelity two qubit gates have been achieved on superconducting circuit platforms in recent years, two qubit gate fidelity remains a limiting factor for algorithm performance in the NISQ era. All microwave gates implemented on fully static architectures are simple to implement and allow for high coherence qubits, but this comes at the expense of always-on couplings and slower gate times. Fully tunable architectures, on the other hand, trade minimal residual coupling and fast entangling operations for increased complexity and sensitivity to flux noise. Parametric entangling gates, which use fast flux modulation to induce resonant interactions in a rotating frame, offer a middle ground between these two approaches to high fidelity two qubit gates. By restricting tunability to a coupling element, qubit sensitivity to flux noise can be significantly reduced and high coherence maintained. Furthermore, the resonant nature of the parametric interactions allow for fast entangling gates with minimal residual coupling. At AQT, we are working towards implementing parametric entangling gates on a 10 qubit quantum processor and investigating how error sources can be mitigated to achieve gate fidelities beyond the current state-of-the-art.

What We Did

Simulations of two qubit gate dynamics, tunable coupler circuits, and the electromagnetic (EM) environment of the chip have guided the design of a new 10 qubit processor — with 9 tunable couplers to mediate parametric interactions between neighboring qubits. This sample builds upon previous work that demonstrates how tunable couplers can be engineered to significantly suppress unwanted static coupling. [1,2] Since parametrically activated gates do not have the strict detuning requirements necessary for optimal cross resonance gates, neighboring qubits can be engineered with large detunings to further suppress any residual static coupling without sacrificing gate speed. This allows for qubits that are well isolated when the coupler is turned “off” and strongly coupled in the presence of parametric driving.

Current Status & Next Steps

Simulations of two qubit gate dynamics have also illustrated the well known trade-off between coherent and incoherent errors as a function of gate speed. Faster gates are less susceptible to the incoherent error caused by qubit relaxation, while slower gates have lower levels of coherent error due to unwanted interactions with the non-computational states of the transmon. Recent improvements in our junction fabrication processes and cryo-packaging have led to the realization of fixed frequency qubits with lifetimes and coherence times in excess of 100 us, allowing us to focus on the mitigation of coherent errors. We have been exploring various pulse shaping protocols, including DRAG and quantum optimal control methods, for mitigating the effects of these parasitic interactions and minimizing coherent gate errors.