This information about the Advanced Quantum Testbed (AQT) at Lawrence Berkeley National Laboratory (Berkeley Lab) is current as of August 2024. If you have any further questions, contact us via email: aqt@lbl.gov.

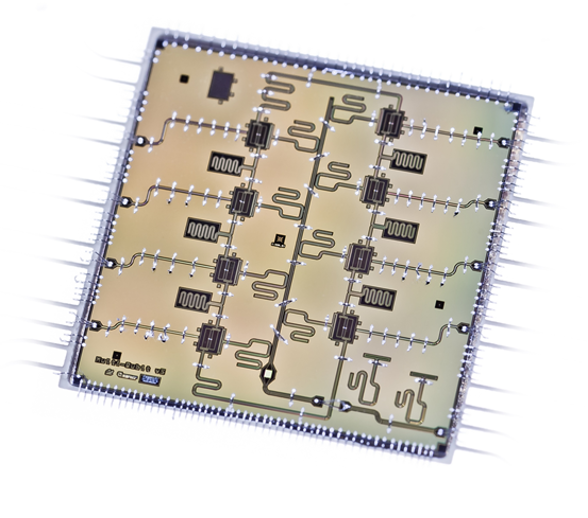

The current QPU available to AQT users is the 8-qubit ring design chip. The specifications and typical parameters for this QPU are:

- Eight transmon qubits in ring, with nearest neighbor connectivity

- Resonance frequency range: 5.2-5.8 GHz

- Typical anharmonicity: 250 MHz

- Multiplexed readout with traveling-wave parametric amplification (TWPA)

- Three-state readout fidelities: >95%

- Coherence times: T1 ~ 100 μs, T2echo ~ 100 μs (with fluctuations)

For detailed information, read: Kreikebaum, J. M., et al. “Improving wafer-scale Josephson junction resistance variation in superconducting quantum coherent circuits.” Superconductor Science and Technology 33.6 (2020): 06LT02

Additionally available is a linearly-connected nine-transmon sample, where the qubits are instead flux-tunable. This processor was developed and fabricated at MIT-Lincoln Laboratories. Specifications:

- Nine transmon qubits, nearest-neighbor connectivity

- Qubit frequencies ranging from 3.3 to 4.8 GHz

- 600-800 MHz tunability for each qubit

- Anharmonicities: 200-210 MHz

- Multiplexed readout

- Coherence times: T1 ~ 10-60 μs, T2echo ~ 10-60 μs

AQT processors with flux-tunable coupling between nearest-neighbors transmons will be available during the following year. Multiple variations of chips are in development and will be released for users progressively throughout the year. Specifications:

- 6-14 transmon qubits in ring, with nearest-neighbor connectivity

- Resonance frequency range: 5-6 GHz

- Typical anharmonicity: 200 MHz

- Multiplexed readout with traveling-wave parametric amplification (TWPA)

- Three-state readout fidelities: >90%

- Coherence times: T1 ~ 40-70 μs, T2echo ~ 40-70 μs (with fluctuations)

Available Gates:

Single-qubit gates:

- Calibrated X90 and virtual Z gates for universal control

- Isolated error rates ~5×10-4, measured by randomized benchmarking (RB)

- Simultaneous error rates 1-2×10-3 per qubit, measured by RB

Cross-resonance gates:

- Nearest-neighbor microwave gates between fixed-frequency qubits

- Typical gate times between 100 to 200 ns

- Controlled-NOT (CNOT) gate error rates ranging from 1% to 4%, measured via interleaved randomized benchmarking (IRB) and cycle benchmarking (CB)

- Novel nearest-neighbor microwave gates between fixed-frequency qubits

- Typical gate times of 200 ns

- CZ error rates: 0.5 – 1% as measured with interleaved RB and CB

Parametric flux-modulation gates

- Created by modulating the frequency of the qubits

- Fermionic simulation (fSim) gate: combination of controlled phase (CZ) and iSWAP

- Gates faster than 100 ns

- CZ error rates below 4%

Qutrit gates:

- Single-qutrit gates with fidelities between 99 to 99.9%

- Two-qutrit CZ gates with fidelities up to 97%

Control Hardware:

Zurich Instruments:

The standard control hardware available to AQT users consists of Zurich Instruments devices. HDAWG units (High Definition Arbitrary Wave Generator) are used for qubit control, operating at 2.4 GSPS with a bandwidth of 750MHz. For qubit readout, we use UHFQA units (Ultra High Frequency Quantum Analyzer), operating at 1.8 GSPS with a bandwidth of 600MHz. Triggering and synchronicity among multiple devices is orchestrated through a PQSC (Programmable Quantum System Controller). This setup enables state-detection on-the-fly, enabling fast reset and fast feedback to less than a microsecond point-to-point.

QubiC:

For more advanced experiments in need of custom functionalities, we have developed the world’s first open source system for control of superconducting quantum computers, dubbed QubiC. Initially developed on the Xilinx VC707 FPGA platform, the current version, QubiC 2.0, is based on the Xilinx ZCU216 RFSoC, with our own custom Analog Front End (AFE) boards, which come in various editions to accommodate both RF and DC-coupled signal needs. QubiC is fully open source, allowing virtually limitless opportunities for modifications at every level of the hardware, firmware/gateware, and software, to meet the needs of custom experiments.

The QubiC 2.0 system is described in a publication here. For more details and documentation, please visit this website.

Advanced functionalities:

- A Distributed Processor architecture on QubiC 2.0 enables Mid-Circuit Measurement and Feedfoward (MCM/FF) with arbitrary logic. This has been used, for example, for first demonstrations of teleportation-based muti-qubit gates described here.

- A lightweight ML implementation on FPGA to allow better readout and state discrimination. This feature is compatible with MCM/FF.

- Hardware-efficient Randomized Compiling allows for mitigation of error at up to one randomization per shot, with zero added cost in terms of execution time. This is performed live on FPGA, and is compatible with MCM/FF without compilation.

- Parameterized Circuit Execution for significant, multi-fold improvements in execution time for experiments where most circuits are structurally equivalent (and only differ by parameters such as phase.) Examples include Cycle Benchmarking and Gate Set Tomography.

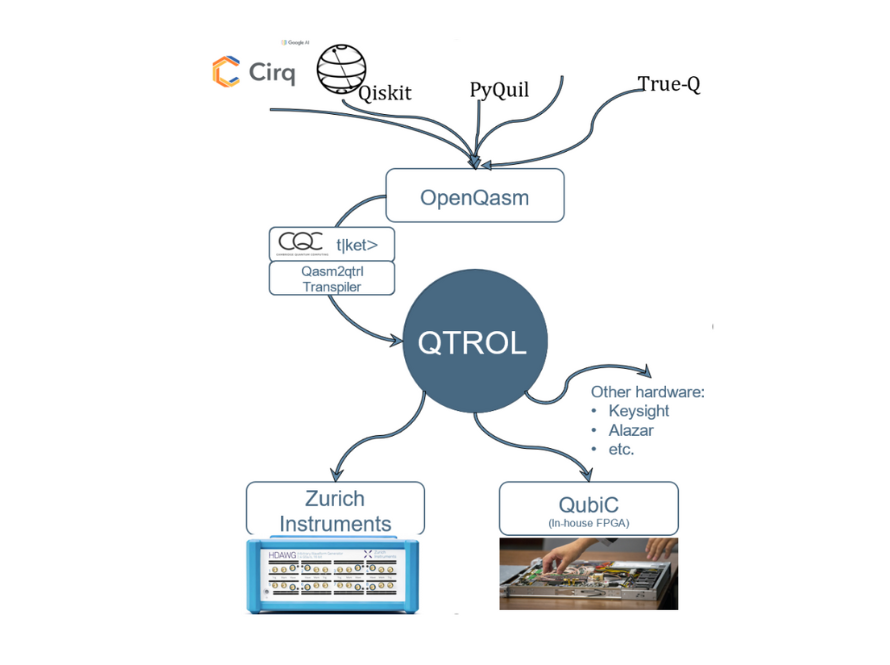

To support QubiC, AQT has developed an early-stage programming stack whose development is ongoing. AQT can accept circuits from widely-used software illustrated at the top of the graph on the right. AQT can work with users to provide access with non-standard software, if required for a project. AQT can also provide access initiated at any starting point in the programming stack, if the circuit is produced in the OpenQasm format, as well as alternate types of access since AQT is developing an in-house instruction set architecture (ISA). From OpenQasm, circuits will be optimized using t|ket> and transpiled into sequences compatible with QTROL, the AQT’s control software, using AQT’s Qasm2qtrol transpiler. QTROL then interfaces with the control hardware to run the experiment. AQT is open to developing specialized software at the QTROL level for nonstandard user software needs. Access to the programming stack can also be provided or developed for users interested in pursuing their own circuit optimization solutions. AQT is open to partnering on projects with users who are interested in co-developing and optimizing the programming stack.